3분 읽기

- 현재 대부분 트랜지스터는 실리콘이나 기타 무기 반도체로 제작.

- 1㎟당 1억 개 이상의 트랜지스터 밀도를 달성하기 위해 마이크로칩의 회로는 적층

- 실리콘 마이크로칩과 달리, 하이브리드 칩은 금속 산화물 반도체와 유기 반도체 결합

- 기존보다 3배 더 많은 양. 적층칩은 총 41개의 서로 다른 반도체 층과 전극으로 구성

- 플렉서블 전자 기기, 사물 인터넷 분야의 소형화에 중요한 기여

트랜지스터는 오늘날 기술에 필수적인 요소다. 전기적으로 제어 가능한 스위치와 증폭기는 모든 회로와 마이크로칩의 기반을 형성하기 때문이다. 현재 대부분 트랜지스터는 실리콘이나 기타 무기 반도체로 제작된다. 1㎟(제곱밀리미터)당 1억 개 이상의 트랜지스터 밀도를 달성하기 위해 최신 마이크로칩의 회로는 여러 층으로 적층된다. 또한 회로 간 거리를 줄여 속도를 높인다.

그러나 단단한 실리콘 마이크로칩은 유연한 전자 장치, 인쇄 회로 또는 생체적합성 전자 장치에는 제한적으로만 적합하다. 금속 산화물 반도체와 고분자 재료로 만들어진 유기 박막 트랜지스터를 결합한 하이브리드 마이크로칩이 더 나은 대안으로 여겨진다.

6중 트랜지스터 스택

연구진은 이러한 하이브리드 마이크로칩으로 새로운 적층 기록을 달성했다. 사우디아라비아 킹 압둘라 과학기술대학교(KAUST)의 사라바난 유바라자(Saravanan Yuvaraja)가 이끄는 연구팀은 최초로 6개의 트랜지스터 스택으로 구성된 하이브리드 CMOS 칩을 제작하는 데 성공했다. 이는 기존보다 3배 더 많은 양이다. 이 새로운 적층 마이크로칩은 총 41개의 서로 다른 반도체 층과 전극으로 구성된다.

특히, 이 적층 마이크로칩은 두 가지 서로 다른 트랜지스터 변형 층이 교대로 배열된 구조다. 첫 번째는 알루미늄으로 만들어진 소스 전극과 n형 도핑된 금속 산화물 반도체인 인듐 산화물로 만들어진 채널을 사용한다. 이는 이러한 반도체에 불순물이 채워져 과잉 전자를 생성한다는 것을 의미한다. 두 번째 트랜지스터 변형은 p-도핑되어 양전하 과잉을 갖는 유기 박막 반도체(C16IDT-BT)로 만들어진 채널을 가지고 있다.

최적화된 접촉 표면

이러한 트랜지스터 유형을 적층하는 데 있어 가장 큰 과제는 층 사이의 접촉점에 있다. 접촉점은 가능한 한 매끄럽고 평평해야 하며, 동시에 개별 트랜지스터는 완벽하게 정렬되어야 한다. "하지만 섀도 마스크 증착이나 아세톤 제거와 같은 일반적인 방법은 종종 거친 모서리를 초래한다"고 유바라자(Yuvaraja)와 그의 동료들은 설명했다. 게이트 전극이 너무 두꺼우면 접촉 표면이 고르지 않을 수도 있다.

이를 방지하기 위해 연구진은 마이크로칩을 위해 40단계로 구성된 최적화된 제조 공정을 개발했다. 특히 알루미늄 전극의 두께를 60nm(나노미터)에서 20nm로 줄였다. 또한, 반도체로 산화인듐(I2O)과 유기 폴리머 파릴렌-C와 같은 재료를 선택함으로써 칩 생산 온도를 150°C 미만으로 낮출 수 있었다고 연구팀은 보고했다.

"수직 적층을 위한 청사진“

"마이크로칩 설계는 항상 더 적은 공간에 더 많은 전력을 집적하는 것이다"며 "제조 공정의 여러 단계를 최적화함으로써, 우리는 수직 적층과 현재의 한계를 훨씬 뛰어넘는 기능 밀도를 위한 청사진을 제공한다"고 말했다. 연구진은 300개와 600개의 트랜지스터로 구성된 회로를 사용한 초기 테스트에서 입력 전압 1V당 94.84V의 이득과 0.47㎼(마이크로와트)의 비교적 낮은 전력 소비를 보였다고 보고했다.

연구진은 또한 적층된 마이크로칩을 사용하여 NOR 및 NAND 회로 형태의 3차원 논리 게이트를 이미 구축했다. 그들은 이러한 하이브리드 3D 마이크로칩이 전자 기기, 특히 플렉서블 전자 기기, 스마트 헬스케어 시스템, 사물 인터넷 분야의 소형화에 중요한 기여를 할 것으로 기대한다.

참고: Nature Electronics, 2025; doi: 10.1038/s41928-025-01469-0

출처: King Abdullah University of Science & Technology (KAUST)

- 현재 대부분 트랜지스터는 실리콘이나 기타 무기 반도체로 제작.

- 1㎟당 1억 개 이상의 트랜지스터 밀도를 달성하기 위해 마이크로칩의 회로는 적층

- 실리콘 마이크로칩과 달리, 하이브리드 칩은 금속 산화물 반도체와 유기 반도체 결합

- 기존보다 3배 더 많은 양. 적층칩은 총 41개의 서로 다른 반도체 층과 전극으로 구성

- 플렉서블 전자 기기, 사물 인터넷 분야의 소형화에 중요한 기여

최초의 6층 하이브리드 마이크로칩

연구진, 6개의 트랜지스터 층을 적층한 최초의 복합 칩 개발

새롭게 개발된 하이브리드 마이크로칩은 기존보다 3배 더 많은 6개의 트랜지스터 층을 적층했다. 기존의 실리콘 마이크로칩과 달리, 이 기록적인 하이브리드 칩은 금속 산화물 반도체와 유기 반도체를 결합했다. 연구팀은 "Nature Electronics"에 발표한 논문에서, 이를 통해 다층 마이크로칩의 성능을 향상시키고 대형의 유연한 전자 응용 분야에 활용할 수 있다고 밝혔다.

|

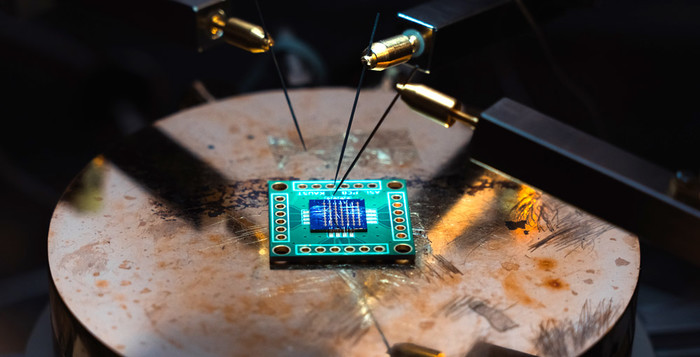

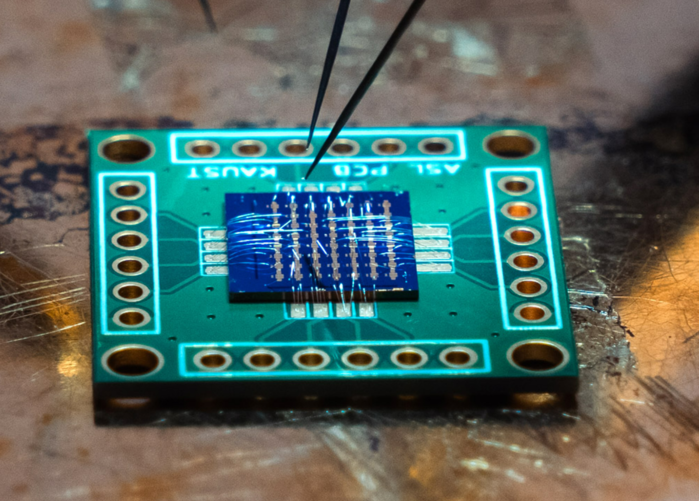

| ▲ 이 하이브리드 마이크로칩은 6개의 트랜지스터 스택으로 구성되어 있으며, 이는 새로운 기록이다. © KAUST |

트랜지스터는 오늘날 기술에 필수적인 요소다. 전기적으로 제어 가능한 스위치와 증폭기는 모든 회로와 마이크로칩의 기반을 형성하기 때문이다. 현재 대부분 트랜지스터는 실리콘이나 기타 무기 반도체로 제작된다. 1㎟(제곱밀리미터)당 1억 개 이상의 트랜지스터 밀도를 달성하기 위해 최신 마이크로칩의 회로는 여러 층으로 적층된다. 또한 회로 간 거리를 줄여 속도를 높인다.

그러나 단단한 실리콘 마이크로칩은 유연한 전자 장치, 인쇄 회로 또는 생체적합성 전자 장치에는 제한적으로만 적합하다. 금속 산화물 반도체와 고분자 재료로 만들어진 유기 박막 트랜지스터를 결합한 하이브리드 마이크로칩이 더 나은 대안으로 여겨진다.

|

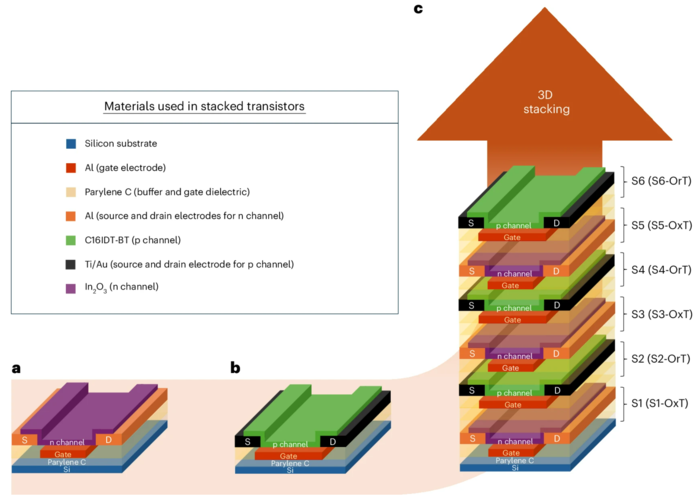

| ▲ a, 실리콘 기판 위에 제작된 OxT의 구조. 이 소자는 Al 게이트 전극, 파릴렌 C 버퍼 및 게이트 유전체, In2O3 n채널 반도체, 그리고 Al 소스(S)/드레인(D) 전극을 포함합니다. b, a와 유사한 게이트 스택을 갖는 OrT의 구조. 단, 채널 전극으로 p형 반도체 C16IDT-BT를 사용하고 S/D 전극으로 Ti/Au를 사용한다. c, OxT와 OrT를 교대로 결합하여 3D 하이브리드 상보형 트랜지스터 구조를 형성하는 6개의 수직 집적 트랜지스터 스택의 개략도. 스택 S1, S3, S5는 n형 OxT이고, 스택 S2, S4, S6은 p형 OrT입니다. 파릴렌 C는 층간 유전체로 사용되어 순차적인 층별 제조 과정에서 전기적 절연과 표면 평탄성을 유지한다. (출처: Published: 17 October 2025 / Three-dimensional integrated hybrid complementary circuits for large-area electronics / nature electronics) |

6중 트랜지스터 스택

연구진은 이러한 하이브리드 마이크로칩으로 새로운 적층 기록을 달성했다. 사우디아라비아 킹 압둘라 과학기술대학교(KAUST)의 사라바난 유바라자(Saravanan Yuvaraja)가 이끄는 연구팀은 최초로 6개의 트랜지스터 스택으로 구성된 하이브리드 CMOS 칩을 제작하는 데 성공했다. 이는 기존보다 3배 더 많은 양이다. 이 새로운 적층 마이크로칩은 총 41개의 서로 다른 반도체 층과 전극으로 구성된다.

특히, 이 적층 마이크로칩은 두 가지 서로 다른 트랜지스터 변형 층이 교대로 배열된 구조다. 첫 번째는 알루미늄으로 만들어진 소스 전극과 n형 도핑된 금속 산화물 반도체인 인듐 산화물로 만들어진 채널을 사용한다. 이는 이러한 반도체에 불순물이 채워져 과잉 전자를 생성한다는 것을 의미한다. 두 번째 트랜지스터 변형은 p-도핑되어 양전하 과잉을 갖는 유기 박막 반도체(C16IDT-BT)로 만들어진 채널을 가지고 있다.

최적화된 접촉 표면

이러한 트랜지스터 유형을 적층하는 데 있어 가장 큰 과제는 층 사이의 접촉점에 있다. 접촉점은 가능한 한 매끄럽고 평평해야 하며, 동시에 개별 트랜지스터는 완벽하게 정렬되어야 한다. "하지만 섀도 마스크 증착이나 아세톤 제거와 같은 일반적인 방법은 종종 거친 모서리를 초래한다"고 유바라자(Yuvaraja)와 그의 동료들은 설명했다. 게이트 전극이 너무 두꺼우면 접촉 표면이 고르지 않을 수도 있다.

|

| ▲ 하이브리드 3D 마이크로칩은 유연한 전자 장치를 비롯한 다양한 응용 분야의 소형화를 앞당길 수 있다. © KAUST |

이를 방지하기 위해 연구진은 마이크로칩을 위해 40단계로 구성된 최적화된 제조 공정을 개발했다. 특히 알루미늄 전극의 두께를 60nm(나노미터)에서 20nm로 줄였다. 또한, 반도체로 산화인듐(I2O)과 유기 폴리머 파릴렌-C와 같은 재료를 선택함으로써 칩 생산 온도를 150°C 미만으로 낮출 수 있었다고 연구팀은 보고했다.

"수직 적층을 위한 청사진“

"마이크로칩 설계는 항상 더 적은 공간에 더 많은 전력을 집적하는 것이다"며 "제조 공정의 여러 단계를 최적화함으로써, 우리는 수직 적층과 현재의 한계를 훨씬 뛰어넘는 기능 밀도를 위한 청사진을 제공한다"고 말했다. 연구진은 300개와 600개의 트랜지스터로 구성된 회로를 사용한 초기 테스트에서 입력 전압 1V당 94.84V의 이득과 0.47㎼(마이크로와트)의 비교적 낮은 전력 소비를 보였다고 보고했다.

연구진은 또한 적층된 마이크로칩을 사용하여 NOR 및 NAND 회로 형태의 3차원 논리 게이트를 이미 구축했다. 그들은 이러한 하이브리드 3D 마이크로칩이 전자 기기, 특히 플렉서블 전자 기기, 스마트 헬스케어 시스템, 사물 인터넷 분야의 소형화에 중요한 기여를 할 것으로 기대한다.

참고: Nature Electronics, 2025; doi: 10.1038/s41928-025-01469-0

출처: King Abdullah University of Science & Technology (KAUST)

[더사이언스플러스=문광주 기자]

[저작권자ⓒ the SCIENCE plus. 무단전재-재배포 금지]

주요기사

+

많이 본 기사

Basic Science

+

AI & Tech

+

Photos

+